#### **Status of the SIR program for TELIS**

V.P. Koshelets, Institute of Radio Engineering and Electronics

#### **List of participants**

#### P.N. Dmitriev, A.B. Ermakov, L.V. Filippenko, O.V. Koryukin, I.L. Lapitskaya, S.V. Shitov, A.S. Sobolev, M.Yu. Torgashin

Institute of Radio Engineering and Electronics (IREE), Moscow, Russia

#### R. Hoogeveen, W.J. Vreeling, P. Yagoubov

National Institute for Space Research (SRON), the Netherlands

# Status of the SIR program for TELIS Outline

- TELIS requirements for SIR channel. Concepts of PL SIR for TELIS

- Design of SIR for TELIS

- FFO for TELIS, PL operation

- Optimization of HM design and regimes

- Computer control of SIR operation

- First test results of T2 SIR

- Conclusion

# Main parameters of TELIS-SIR spectrometer

| ## | Description                                                                                   | Base line | Goal    |

|----|-----------------------------------------------------------------------------------------------|-----------|---------|

| 1  | Input frequency range, GHz                                                                    | 600 - 650 | 500-650 |

| 2  | Minimum noise temperature in the range (DSB), K                                               | 200       | 250     |

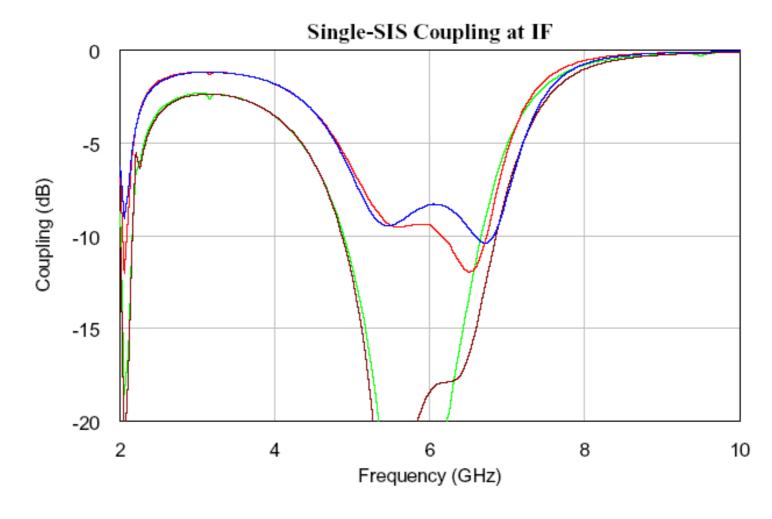

| 3  | Output IF range, GHz                                                                          | 5 - 7     | 4 - 8   |

| 4  | Spectral resolution, MHz                                                                      | 1         | 1       |

| 5  | Contribution to the nearest spectral channel by phased locked FFO (dynamic range), dB         | -20       | -20     |

| 6  | Contribution to a spectral channel by phased locked FFO at 4-8 GHz offset from the carrier, K | 20        | 20      |

| 7  | LO frequency net (distance between nearest settings of the PL FFO frequency), MHz             | < 300     | < 300   |

| 8  | Dissipated power at 4.2 K stage (including IF amplifiers chain), mW                           | 100       | 50      |

| 9  | Operation temperature, K                                                                      | < 4.5     | < 4.5   |

### **Requirements for TELIS-SIR spectrometer**

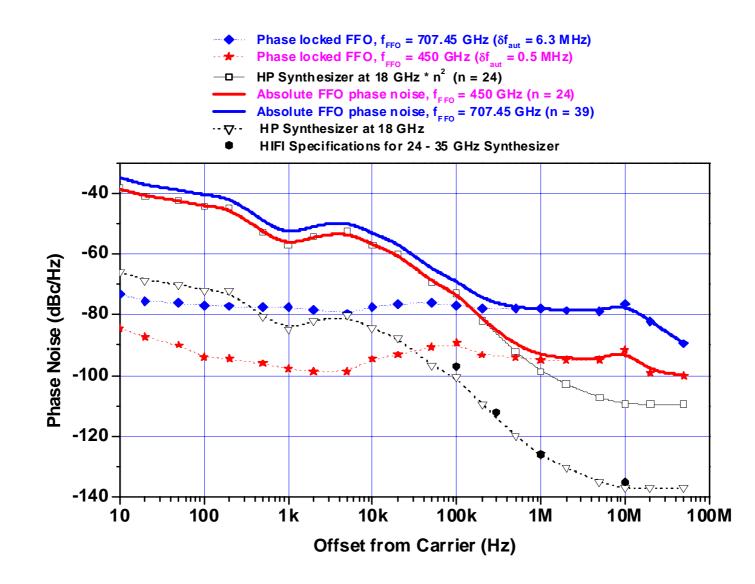

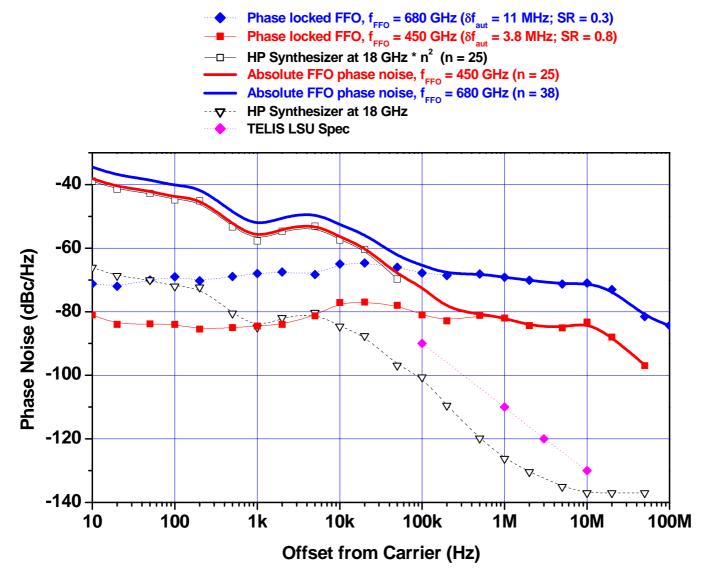

- ## 5 required dynamic range of the spectrometer 20 dB. It corresponds to PL FFO Phase Noise –80 dBc/Hz at the 1 MHz offset from the carrier)

- What about remote channels (10 –100 MHz offset) ? Do we need "1/f reduction" as required for WBS-HIFI ? That corresponds to -100 dBc/Hz at 10 MHz offset !!

- ## 6 Contribution to a spectral channel by phased locked FFO at 4-8 GHz offset from the carrier should be < 10% of SIR Tr (< 20 K). It corresponds to : NCR = 10 log (T<sub>10</sub>\* k<sub>B</sub>) – 10 log ( P<sub>10</sub><sup>opt</sup>) = -152 dBc/Hz

- An additional argument for balanced integrated receiver !

#### Phase Noise of the PL FFO

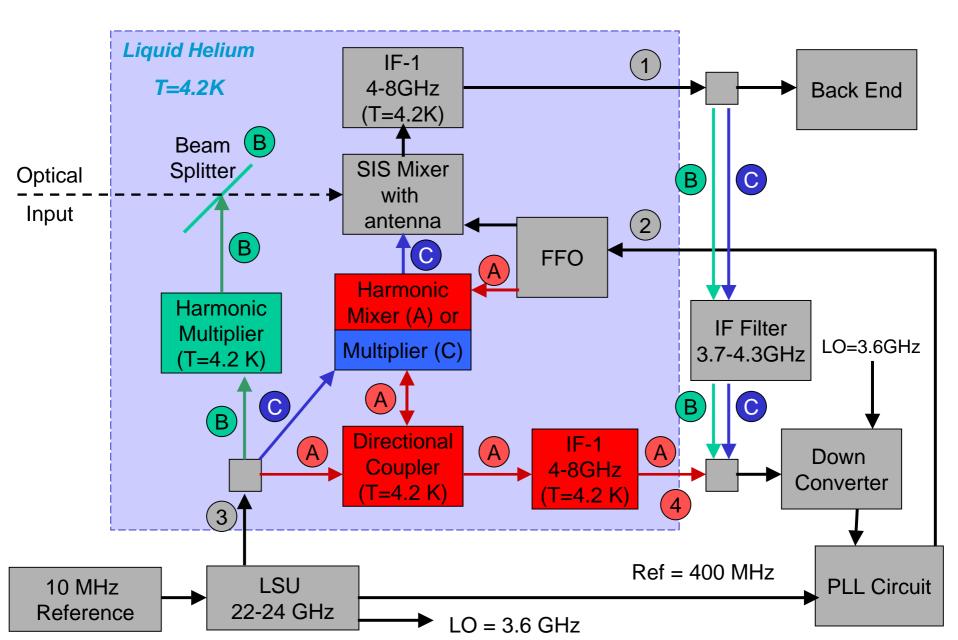

#### **3 Concepts of a SIR with PL FFO**

## Challenges in SIR Design: Requirements

- 500-650 GHz SIS mixer

- SSB Trx < 250 K @ 600-650 GHz

- ➤ Twin-SIS is the most suitable solution

- Wide-band IF (4-8 GHz) coupling circuit

- High capacitance of the structure

#### • LO match & Integration of PLL circuit

- FFO operates above the boundary voltage

- Exact power split at the antenna-mixer

- Minimum power for HM

- > External harmonic generator as a safe option

#### **Design Novelties: 3-D EM Modeling**

#### **Double-Slot Antenna (DSA) Mixer**

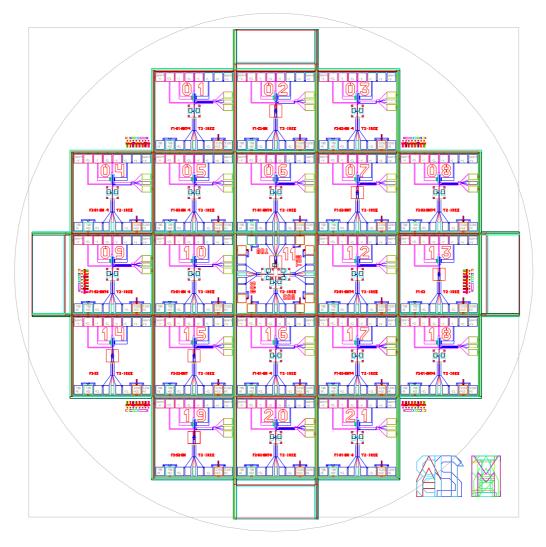

#### Mask Set T2:Wafer Layout

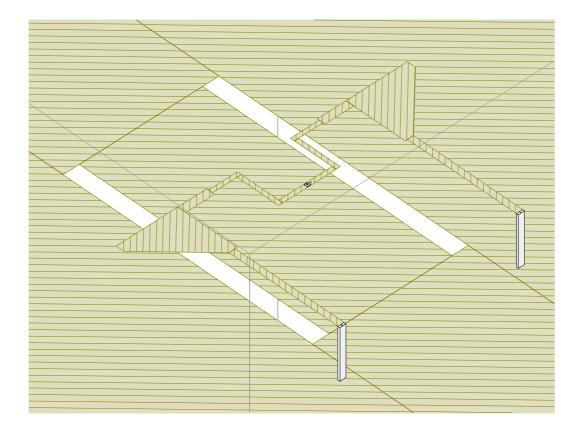

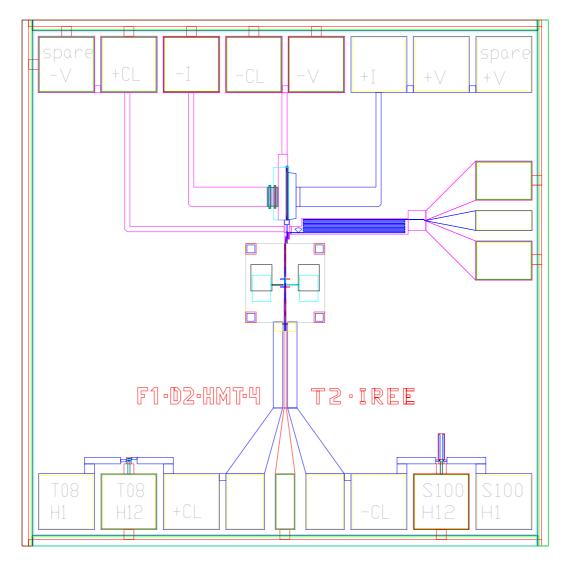

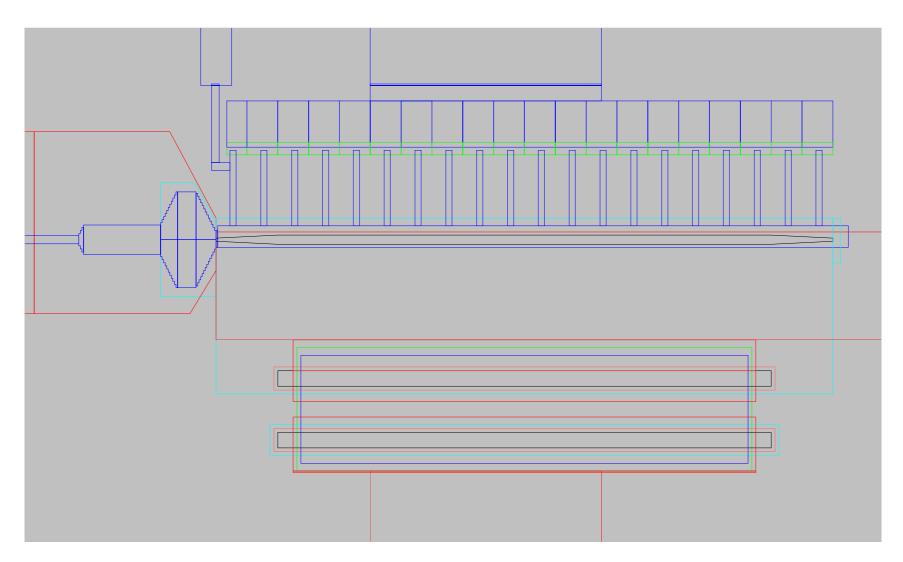

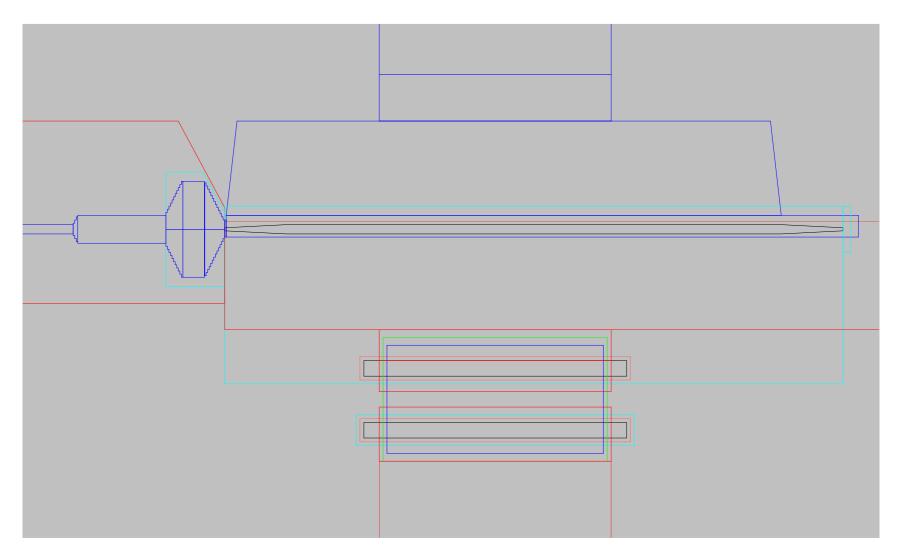

## Mask Set T2: SIR DDA Chip Layout

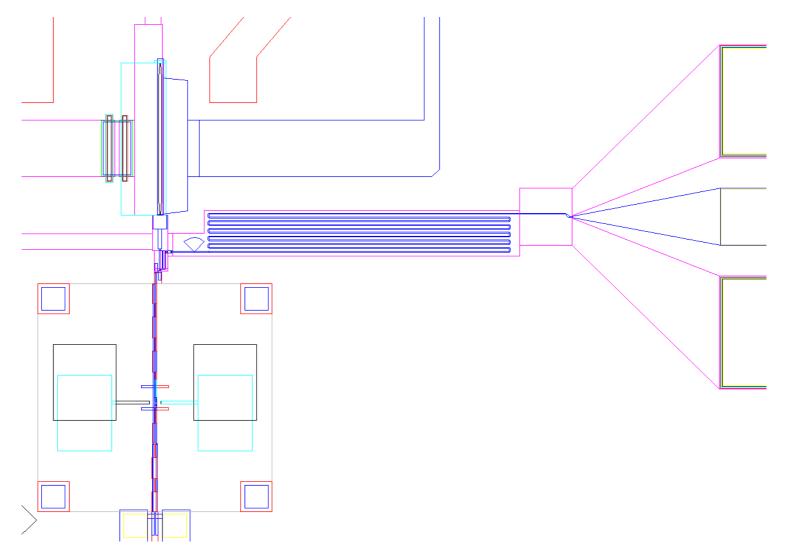

## Mask Set T2: DDA Layout (magnified)

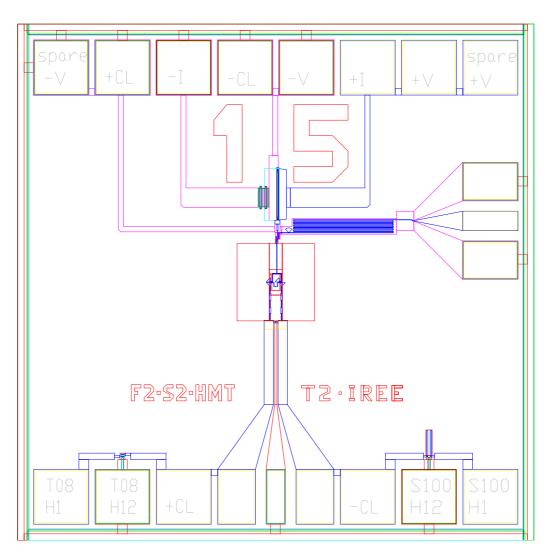

## Mask Set T2: SIR DSA Chip Layout

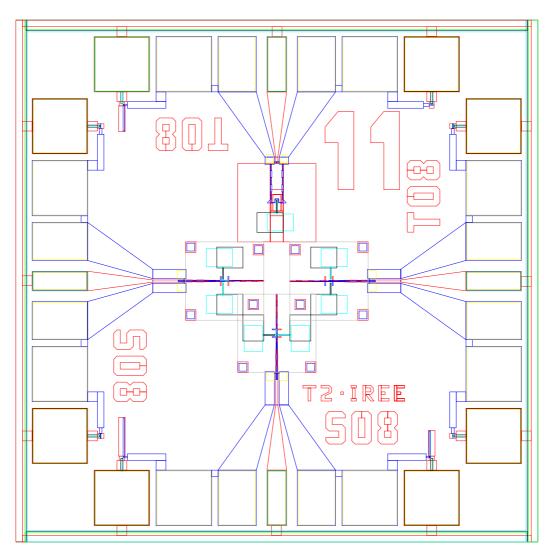

## Mask Set T2: Reference Chip Layout

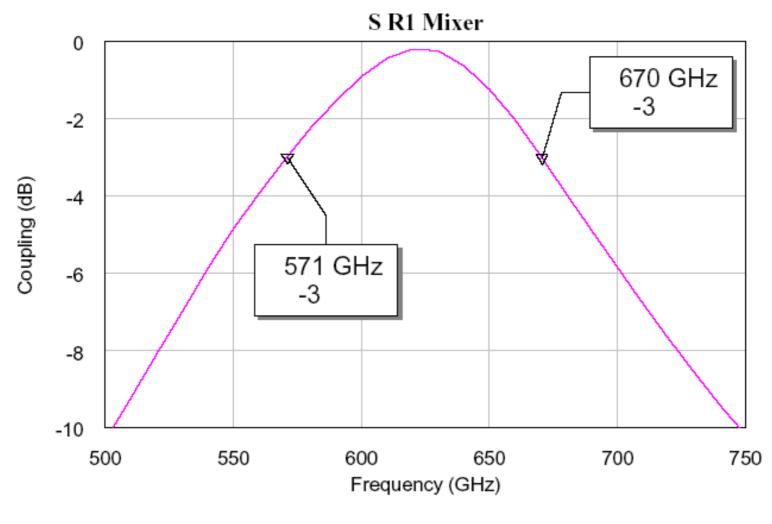

### Numerical Simulations: Single-SIS DDA Mixer

SIR for TELIS

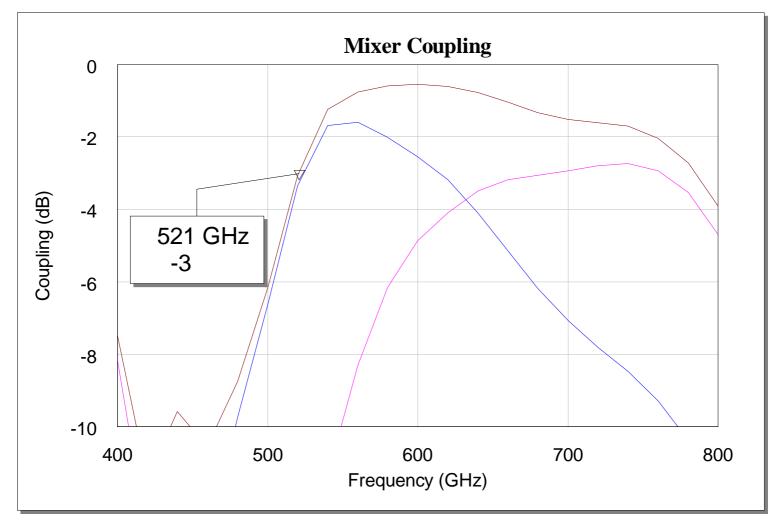

## Numerical Simulations: Twin-SIS DDA Mixer

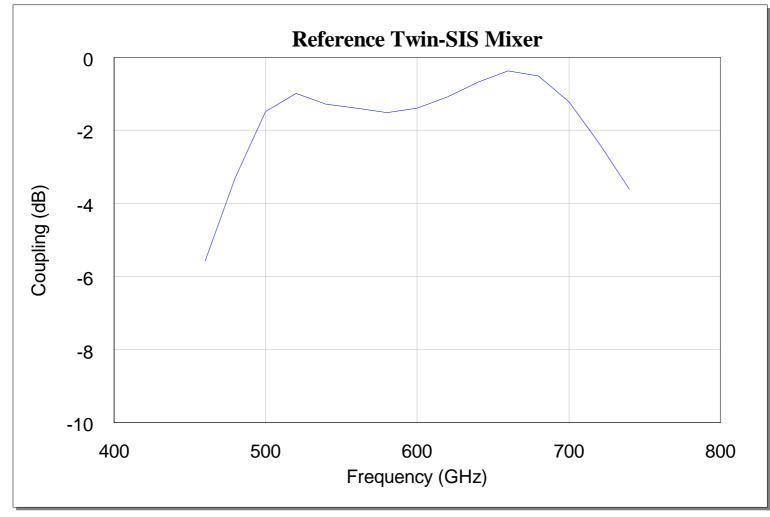

## Numerical Simulations: Twin-SIS DSA Mixer

## Numerical Simulations: IF Connection of the Chip

Y Axis

Axis

## Numerical Simulations: IF Connection of the Chip

SIR for TELIS

# FFO for TELIS (Outline)

- FFO power ( dependence on design)

- FFO linewidth (dependence on design, FFO frequency and current density)

- → FFO for T-2

- PLL results

- FFO IVCs reproducibility, other issues

- Conclusion

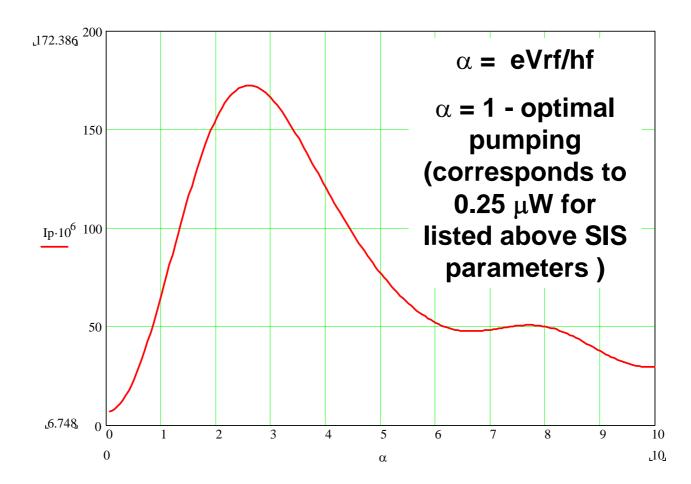

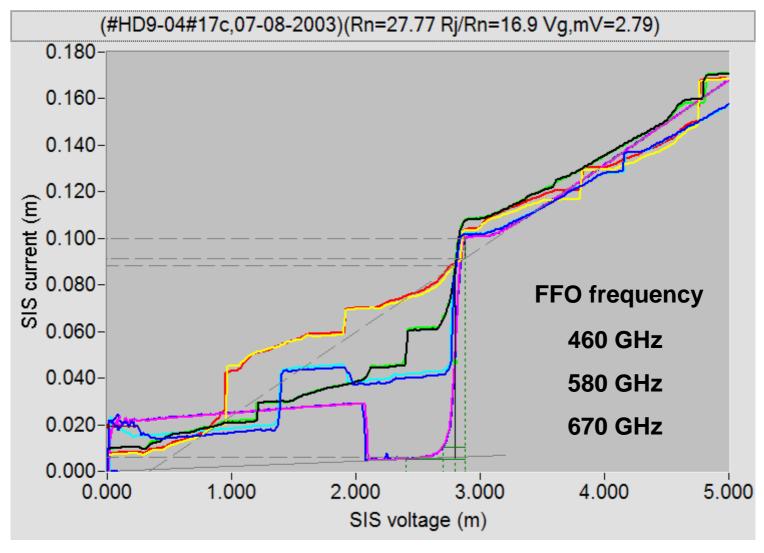

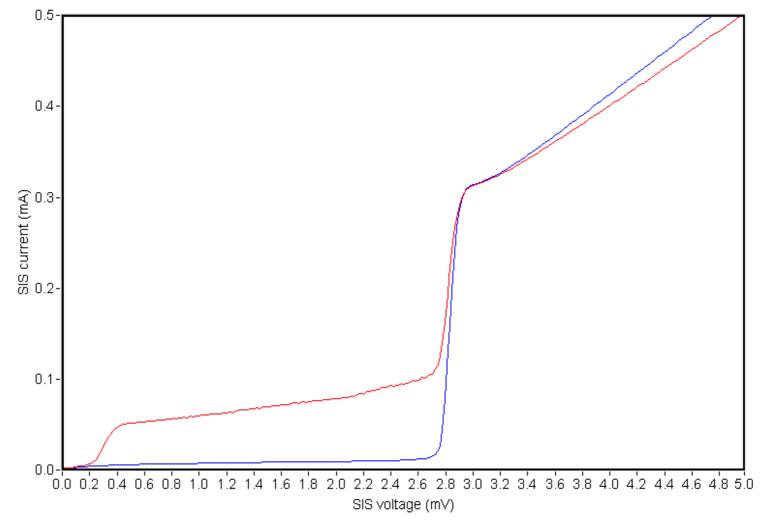

## Calculated IVCs of SIS mixer at different levels of power, delivered to mixer at 500 GHz

SIR for TELIS

Dependence of the current on photon induced step on power  $R_n = 15 \Omega; R_nS = 30 \Omega^*\mu^2; f = 500 \text{ GHz}; \text{Vsis} = 2.5 \text{ mV}$

SIR for TELIS

## HD7-09#02 (RnS = 26 $\Omega * \mu^2$ )

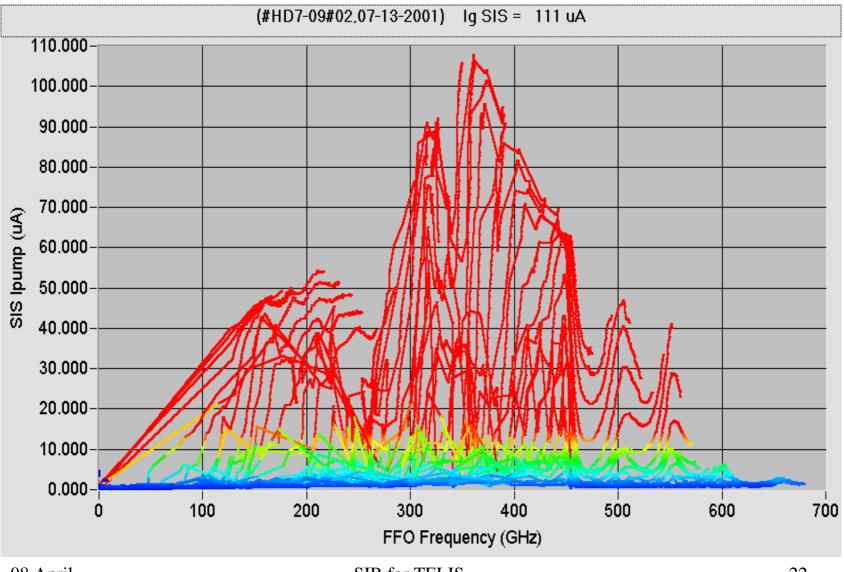

# SIS Pumping by FFO (HD7 & T1 design)

# New FFO design HD9 with distributed bias

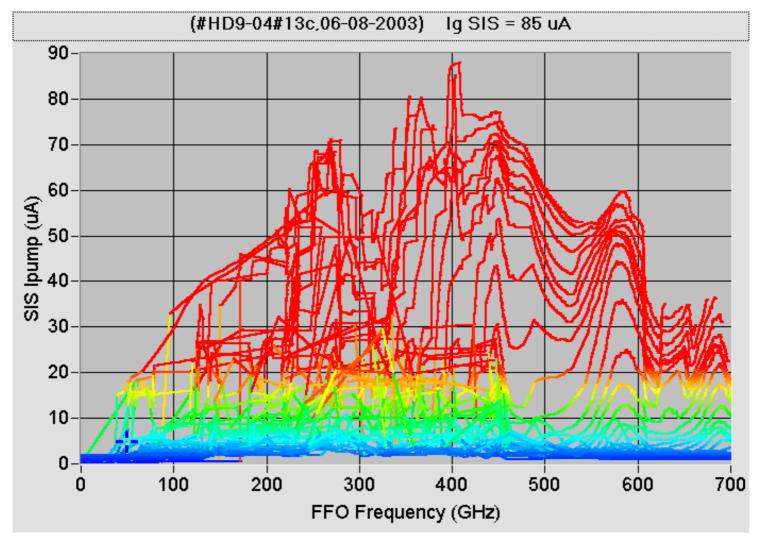

# HD9-04#13 (RnS = 37 $\Omega * \mu^2$ )

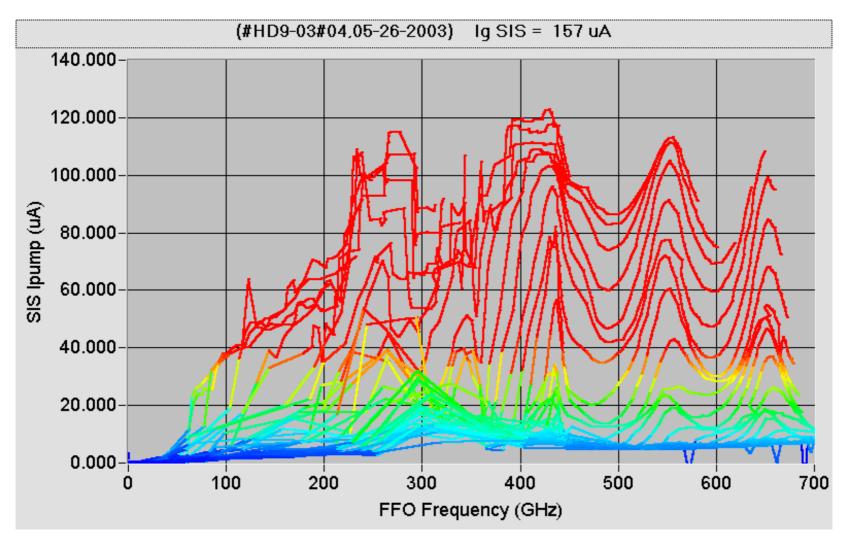

## HD9-03-04 (RnS = 27.5 $\Omega * \mu^2$ )

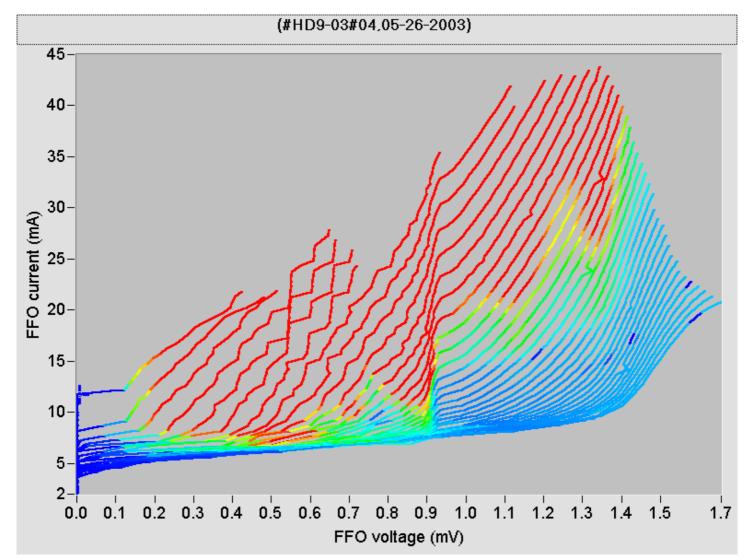

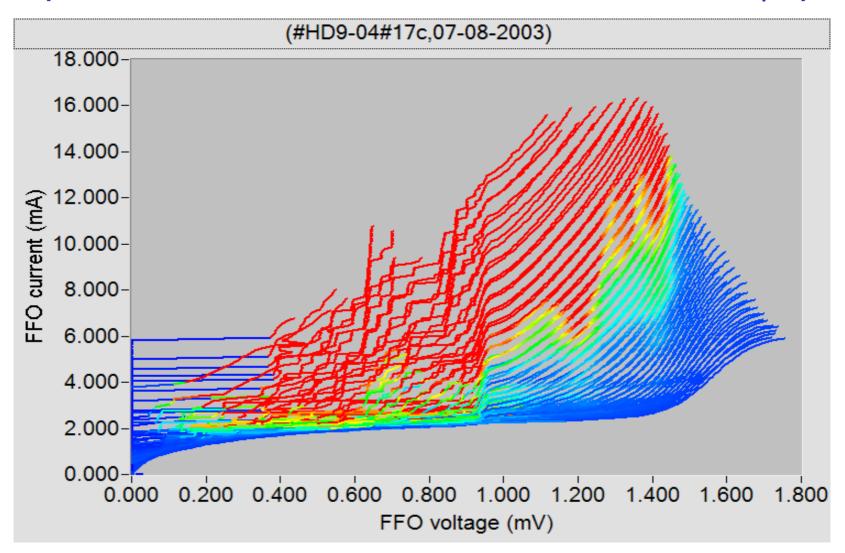

# **FFO IVCs** - **HD9-03-04** (RnS = 27.5 $\Omega * \mu^2$ )

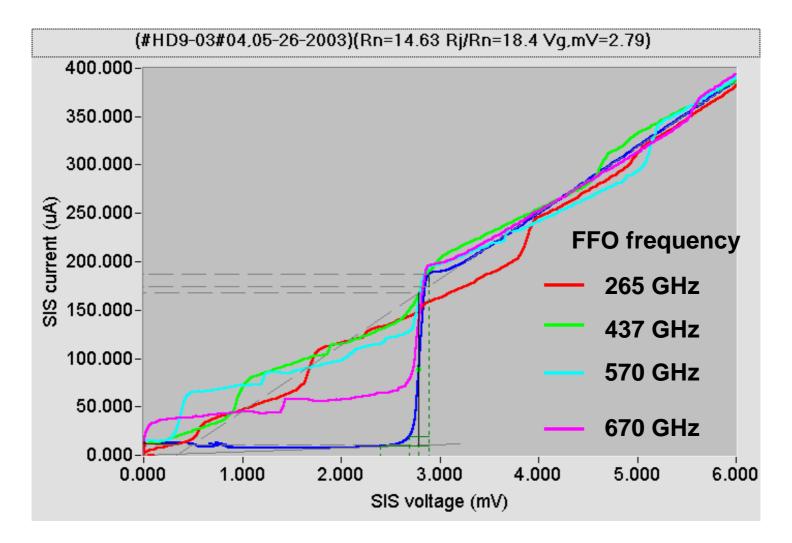

#### HD9-03#04; SIS pumped by FFO RnS = 27.5 $\Omega * \mu^2$

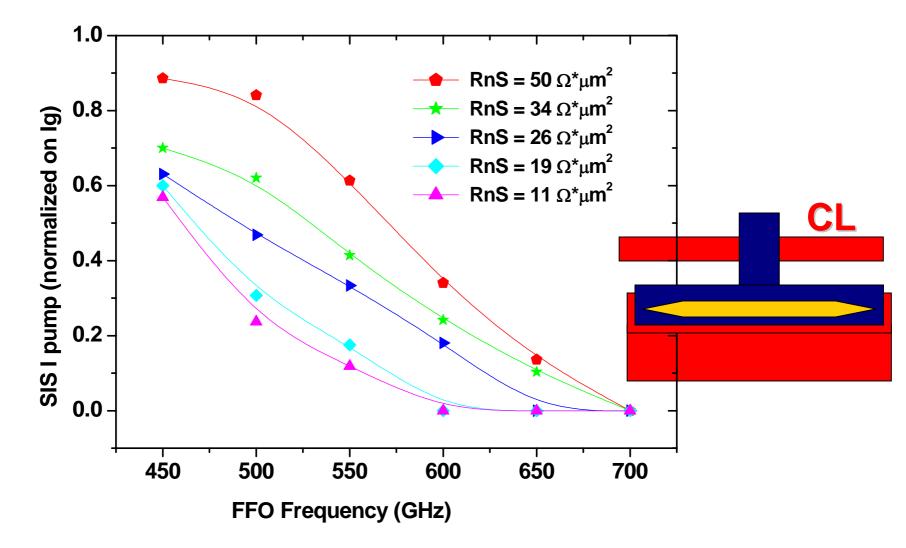

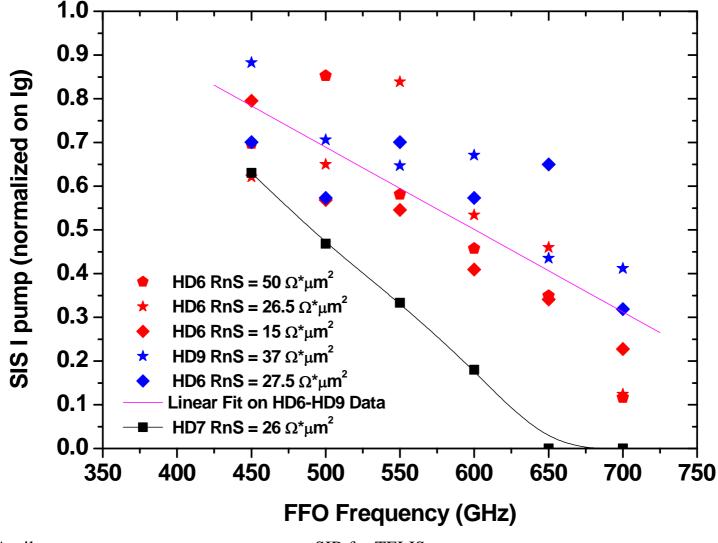

# SIS Pumping by FFO (Different Designs)

SIR for TELIS

## FFO Power delivered to HM and SIS mixer

- Analysis of the results for different FFO designs (including FFO used in T1), which were fabricated with various current density (RnS) has demonstrated that delivered to HM power depends both on FFO design and junctions' RnS.

- Reason of insufficient pumping for T1 circuits at high frequencies and high current density has been found.

- New designs for T2 have been developed and tested, these circuits demonstrate sufficient pumping from 250 to 700 GHz for RnS from 50 to 15 Ω\*µ<sup>2</sup>.

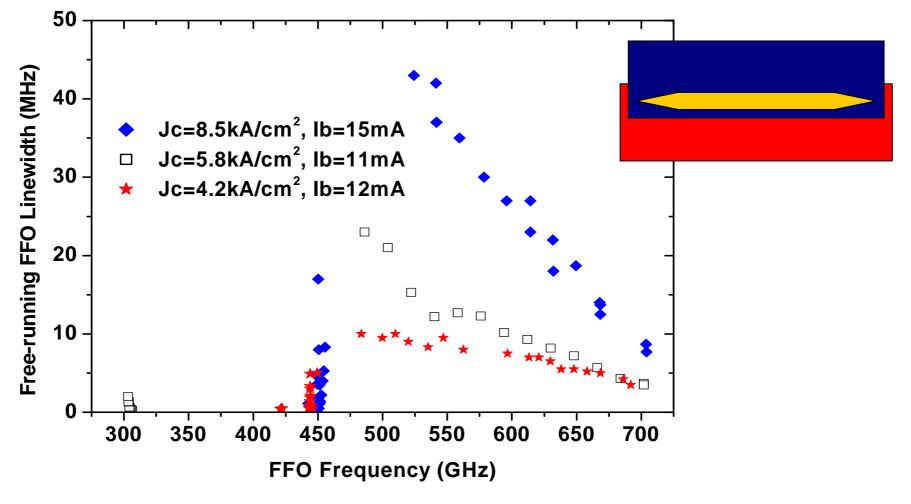

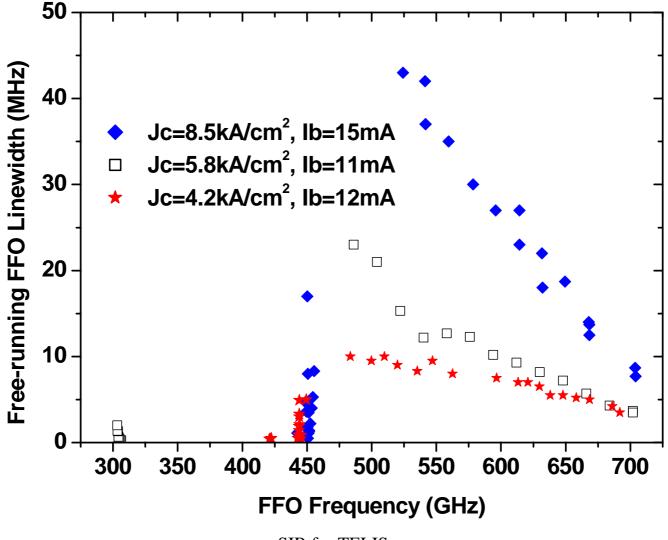

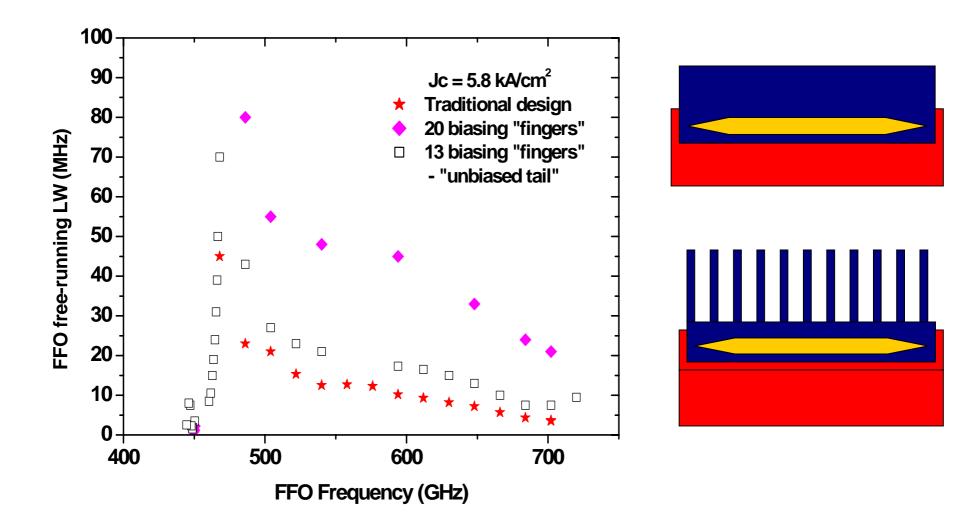

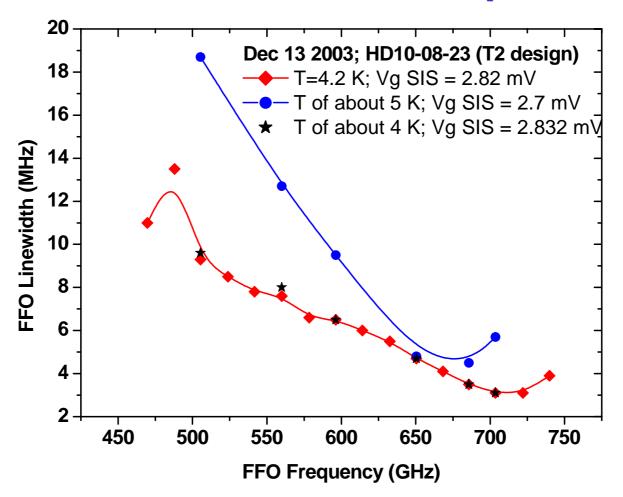

### FFO Linewidth: Dependence on FFO Frequency and Current Density

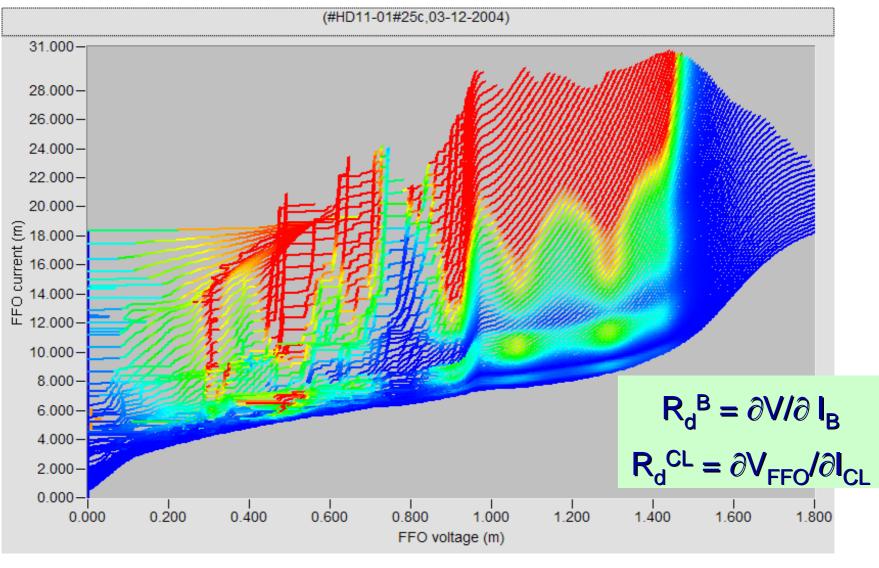

## **IVCs of FFO measured at different Icl**

SIR for TELIS

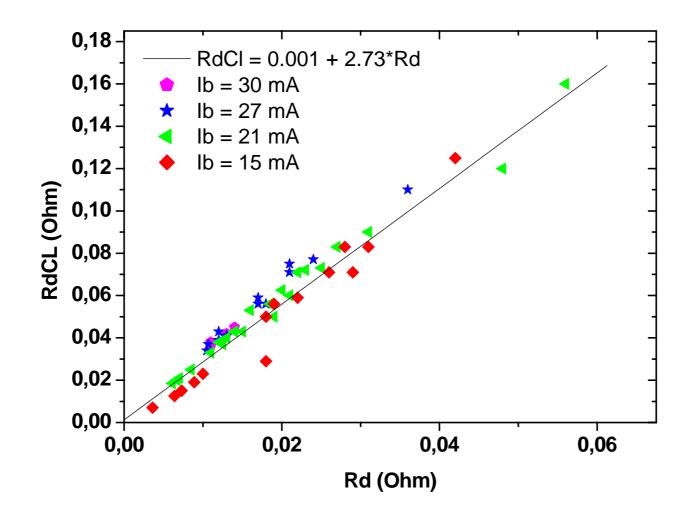

# $R_d^{CL}$ as a function of $R_d$

#### FFO Linewidth: Dependence on FFO Voltage and Current Density

SIR for TELIS

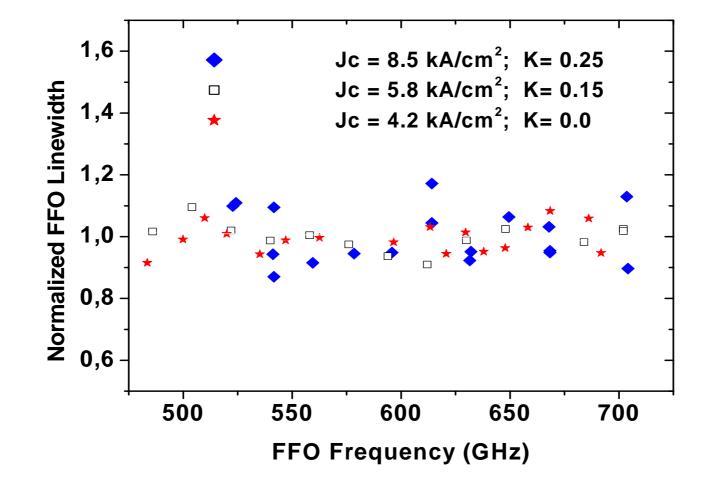

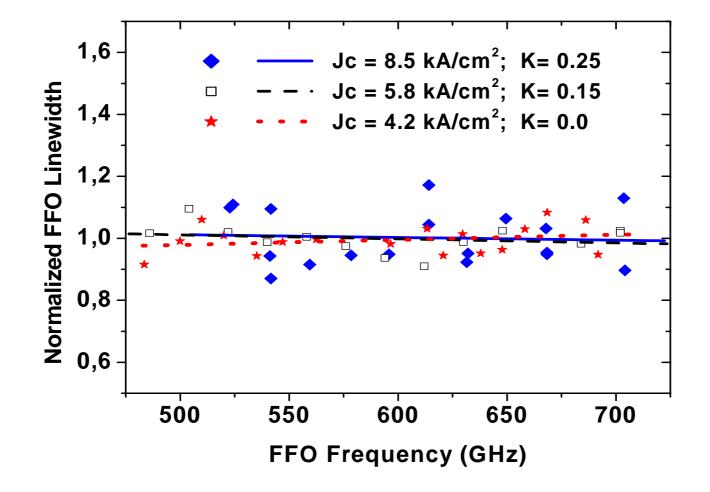

#### **Normalized FFO Linewidth**

$$\Delta \mathbf{f} := \left(\frac{2 \cdot \mathbf{e}}{\mathbf{h}}\right)^2 \cdot \left(\mathbf{R}_{\mathbf{d}} + \mathbf{K} \cdot \mathbf{R}_{\mathbf{d}} \mathbf{CL}\right)^2 \cdot \left[\frac{\mathbf{e} \cdot (\mathbf{lqp})}{2 \cdot \pi} \cdot \mathbf{coth}\left(\frac{\mathbf{e} \cdot \mathbf{V}}{2 \cdot \mathbf{k}_{\mathbf{b}} \cdot \mathbf{T}}\right) + \frac{2 \cdot \mathbf{e} \cdot (\mathbf{ls})}{2 \cdot \pi} \cdot \mathbf{coth}\left(\frac{\mathbf{e} \cdot \mathbf{V}}{\mathbf{k}_{\mathbf{b}} \cdot \mathbf{T}}\right)\right] + \frac{1}{\pi} \cdot \left(\frac{2 \cdot \mathbf{e}}{\mathbf{h}}\right) \cdot \left(\mathbf{R}_{\mathbf{d}} + \mathbf{R}_{\mathbf{d}} \mathbf{CL}\right) \cdot \mathbf{I}_{\mathbf{H}}$$

#### **Normalized FFO Linewidth**

$$\Delta f := \left(\frac{2 \cdot e}{h}\right)^2 \cdot \left(R_d + K \cdot R_{dCL}\right)^2 \cdot \left[\frac{e \cdot (lqp)}{2 \cdot \pi} \cdot \coth\left(\frac{e \cdot V}{2 \cdot k_b \cdot T}\right) + \frac{2 \cdot e \cdot (ls)}{2 \cdot \pi} \cdot \coth\left(\frac{e \cdot V}{k_b \cdot T}\right)\right] + \frac{1}{\pi} \cdot \left(\frac{2 \cdot e}{h}\right) \cdot \left(R_d + R_{dCL}\right) \cdot I_{IL}$$

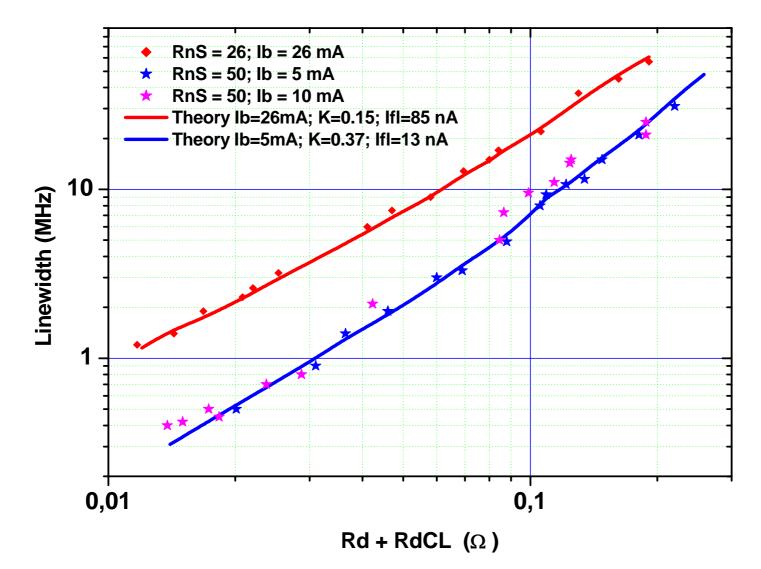

## **FFO Linewidth on (R\_d + R\_d^{CL})**

## **FFO Linewidth (Design issue)**

#### FFO of T2 design with unbiased tail

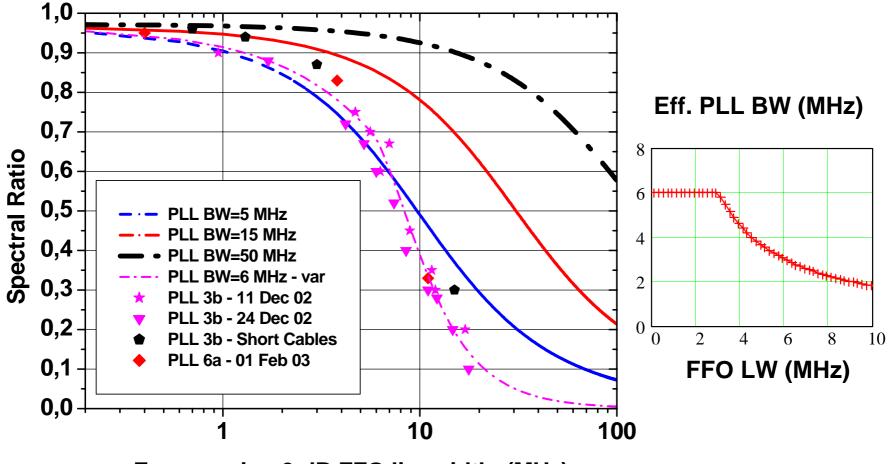

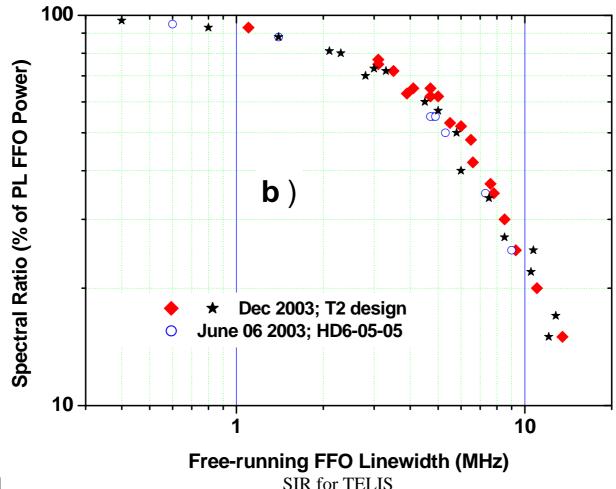

## Ratio of PL and total FFO power

Free running 3 dB FFO linewidth (MHz)

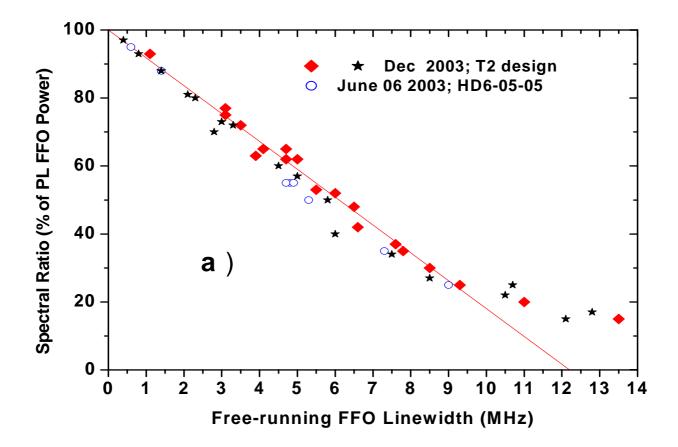

# Spectral Ratio of the PL FFO vs free running FFO linewidth

# Spectral Ratio of the PL FFO vs free running FFO linewidth

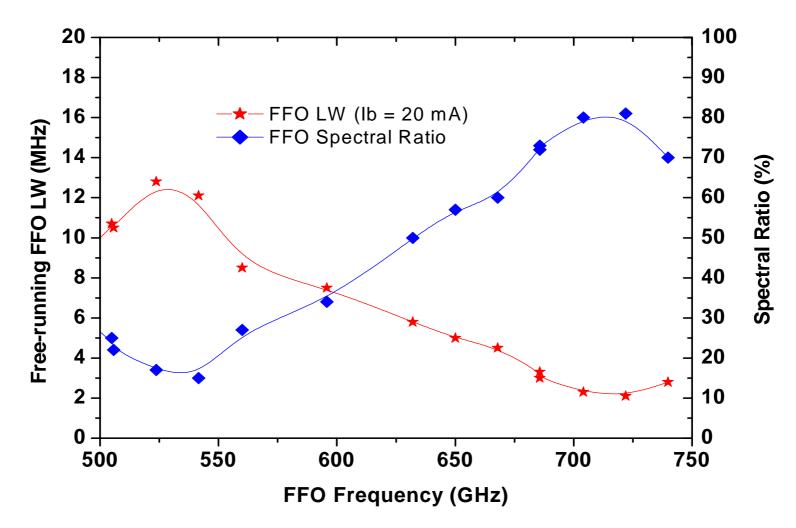

## **FFO LW and SR vs FFO frequency** ( $W_{FFO} = 10 \mu$ ; RnS = 40 $\Omega^* \mu^2$ )

## Phase Noise of the PL FFO (Breadboard)

## FFO linewidth vs FFO frequency, measured at different temperatures

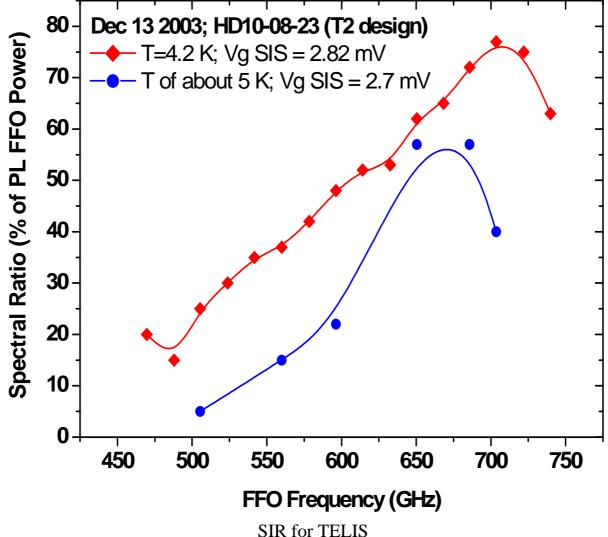

## **Spectral Ratio of the PL FFO vs frequency,** measured at different temperatures

## **FFO Shielding**

- Superconducting shield: stability of the PL FFO at changing of dewar orientation.

- Magnetic / Superconducting shield combination: reproducibility of the FFO state after heating.

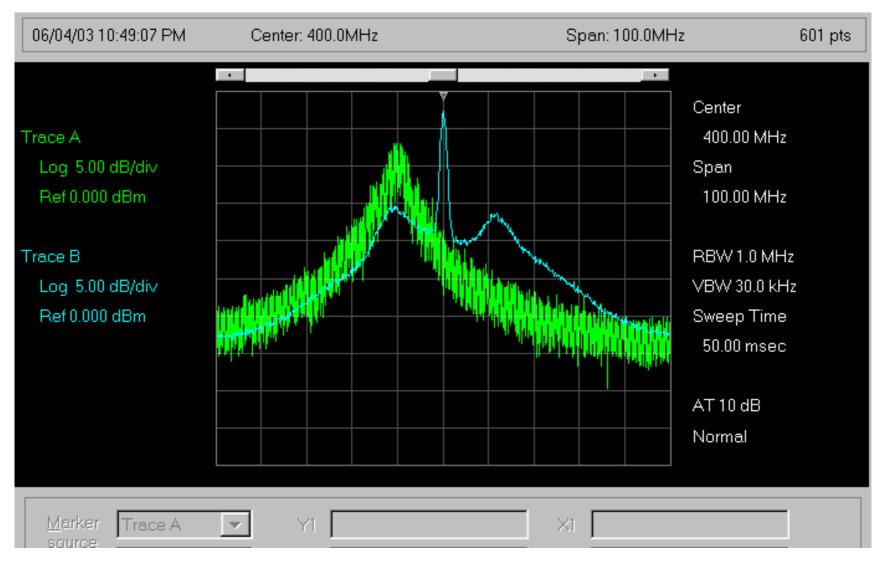

### Free-running and PL FFO Spectra; f FFO = 687 GHz

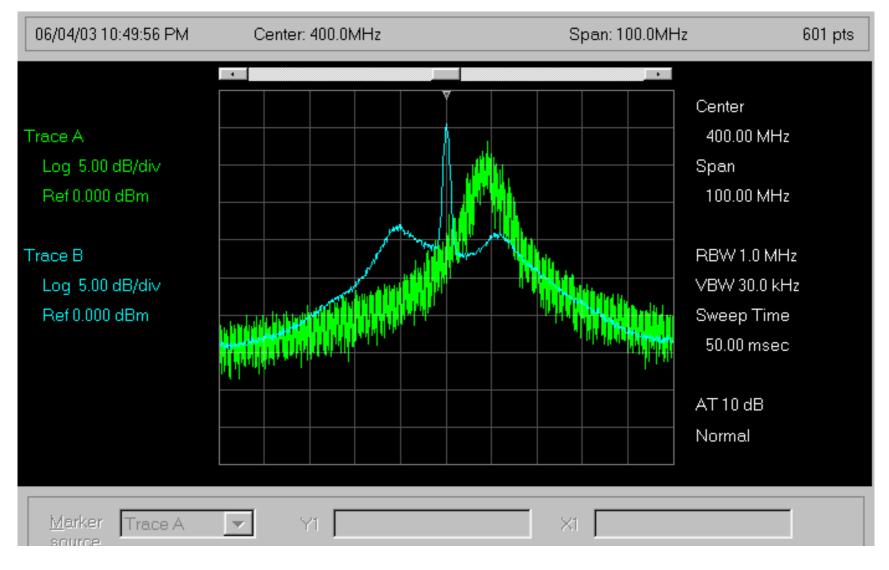

#### Free-running and PL FFO Spectra, dewar rotated on 90 deg

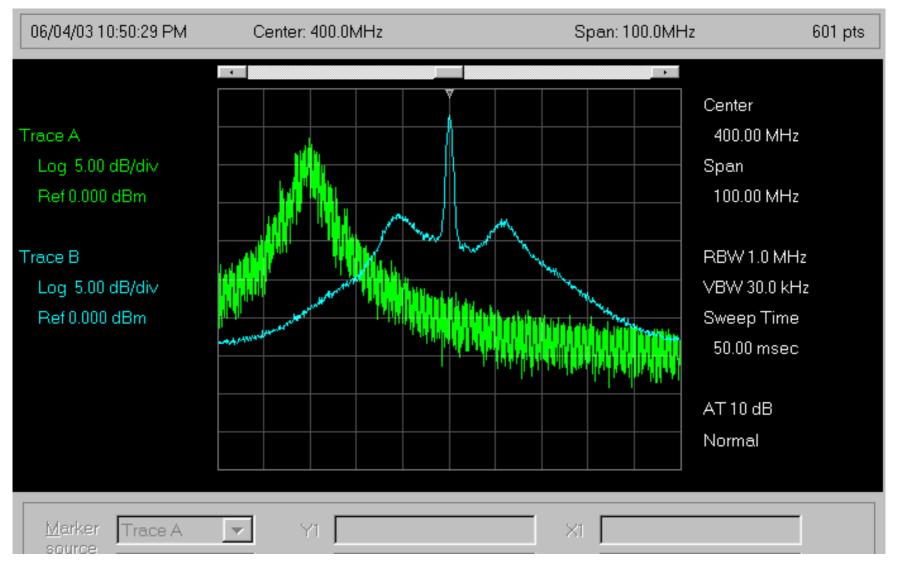

#### Free-running and PL FFO spectra, dewar rotated on - 90 deg

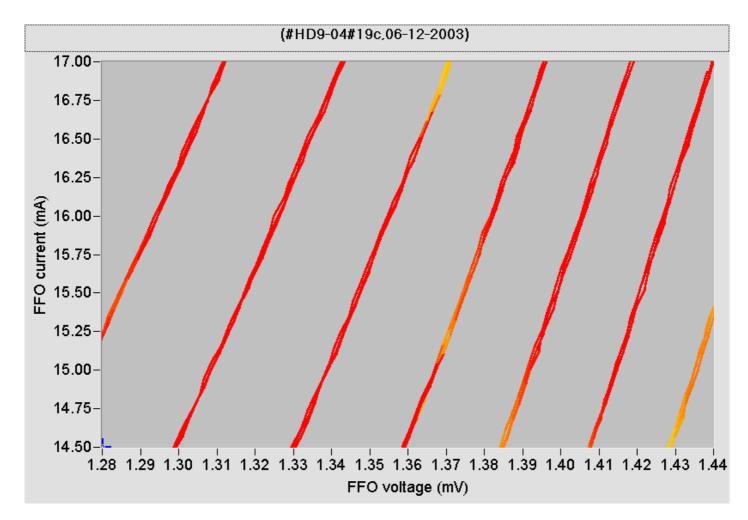

## FFO IVCs measured after 2 consequent thermocyclings ('usual" situation – there is a shift of about 100 μV)

#### Part of the FFO IVCs measured after 3 consequent thermocyclings ('perfect" situation – shift is of about 1 μV)

#### SIS IVCs pumped by FFO measured after 2 consequent thermocyclings

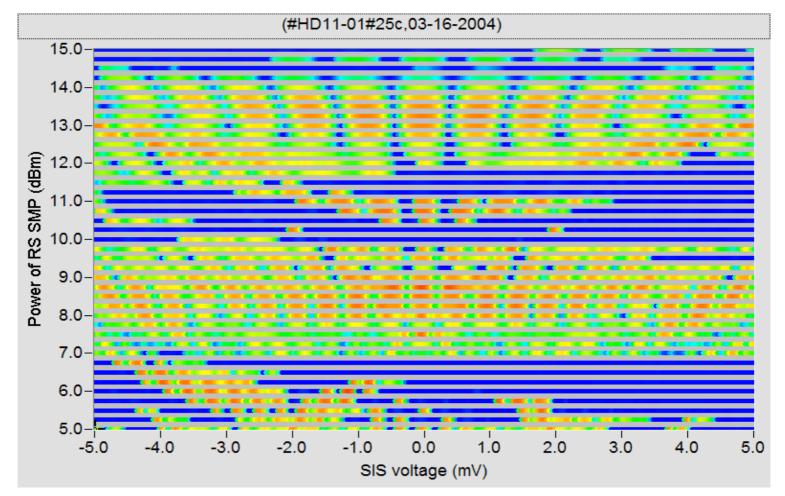

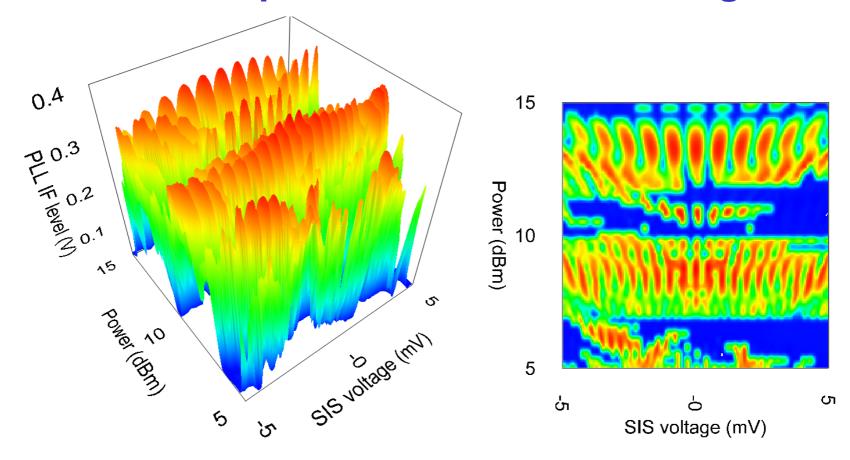

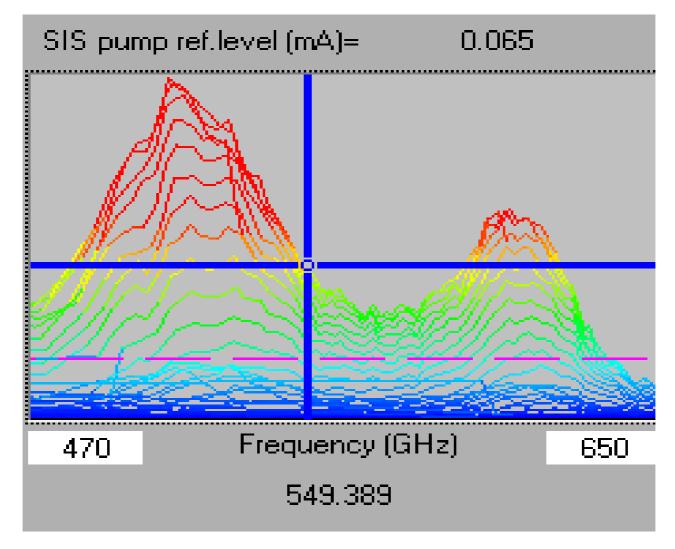

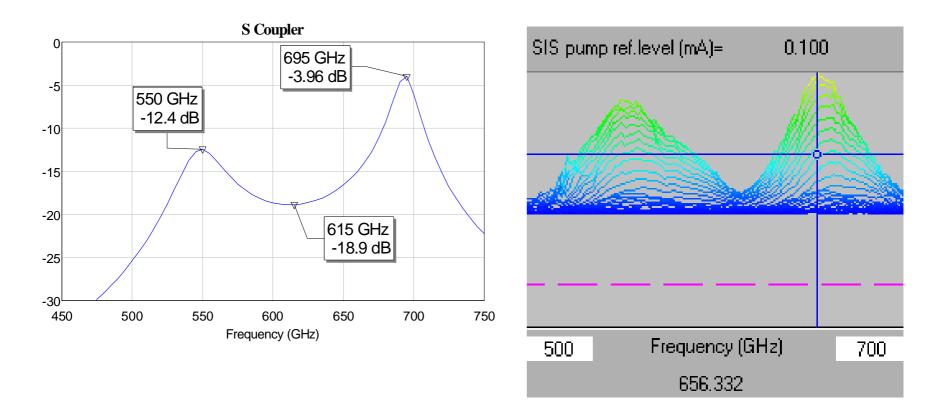

### 2-D diagram for HM operational parameters measured by PC controlled PLL.

The color represents the IF-out PLL signal.

#### 3-D diagram for HM operational parameters measured by PC controlled PLL. The color represents the IF-out PLL signal.

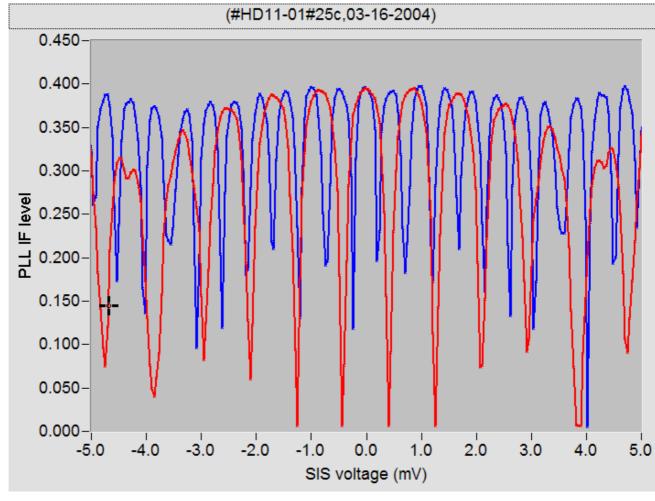

#### Dependence of the PLL\_IF level on HM bias voltage at 2 values of synthesizer power (13.25 dBm – red and 8.5 dBm – blue)

SIR for TELIS

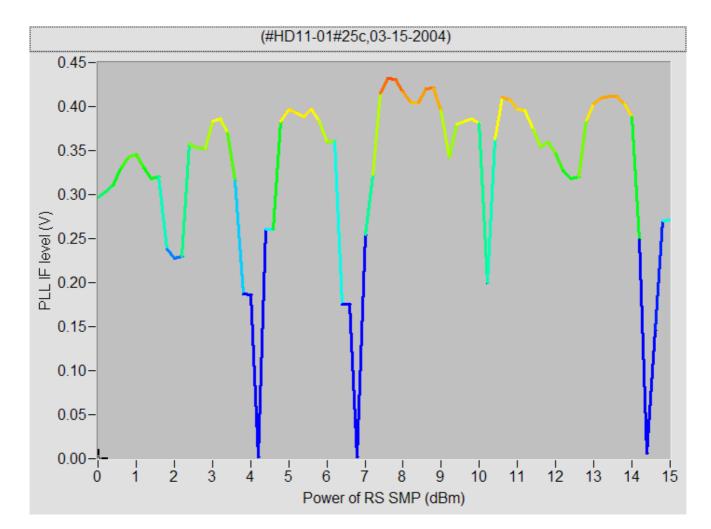

#### Dependence of the PLL\_IF level on synthesizer power at HM bias voltage = 0.0 mV.

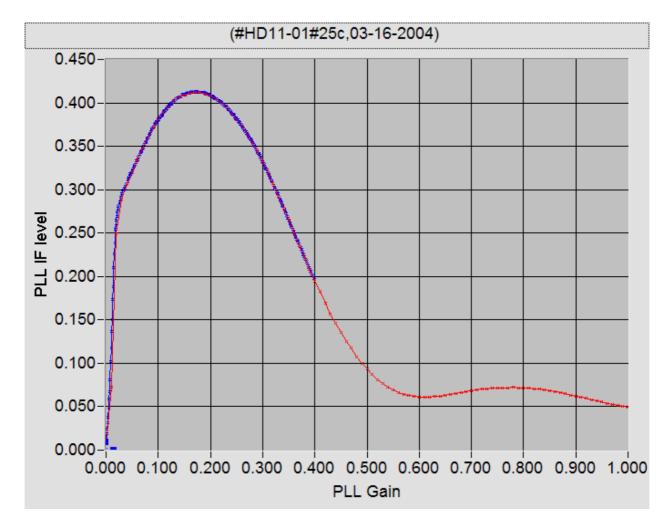

#### Dependence of the PLL\_IF level on the PLL Gain setting

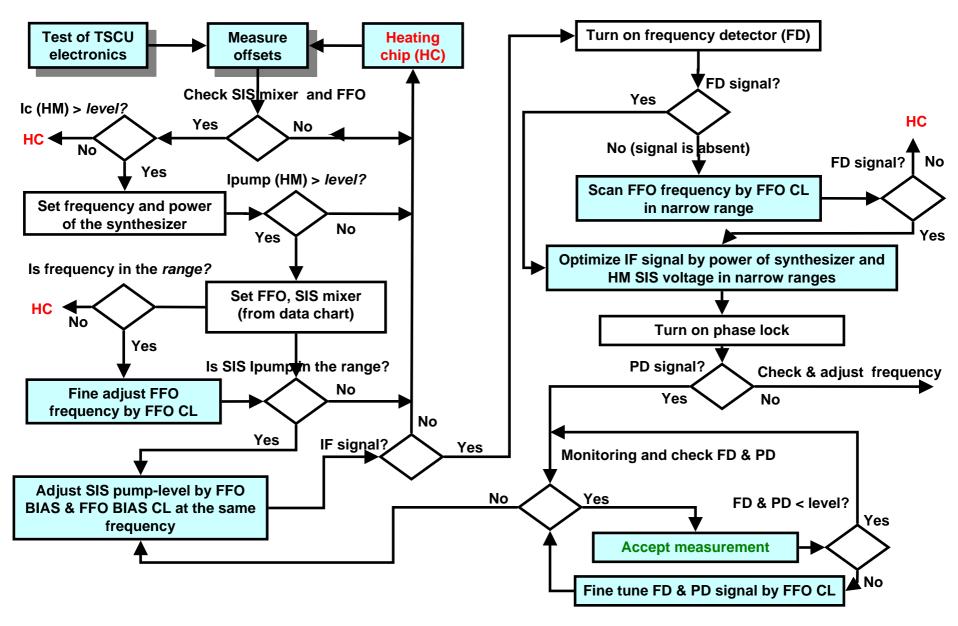

## **Algorithms for TSCU (block diagram)**

## Table of available T2 SIR batches

| #     | Data                  | Substrata                                        | RnS         |       |  |

|-------|-----------------------|--------------------------------------------------|-------------|-------|--|

| #     | Date                  | Substrate                                        | SIS         | FFO   |  |

| T2011 | 20/10/2003-25/10/2003 | Si 300 µm, one side polished                     | 28-30       |       |  |

| T2012 | 20/10/2003-20/10/2003 | Si 300 µm, one side polisited                    |             |       |  |

| T2021 | 27/10/2003-6/11/2003  | Si 300 μm, one side polished                     | 28-30       |       |  |

| T2022 | 21/10/2003-0/11/2003  | Si 300 µm, one side polisited                    |             |       |  |

| T2031 | 31/10/2003-12/11/2003 | Si 300 $\mu$ m one side polished                 | 28-30       |       |  |

| T2032 | 31/10/2003-12/11/2003 | Si Soo µin one side polisited                    |             |       |  |

| T2041 | 13/10/2003-20/10/2003 | /10/2003-20/10/2003 Si 520 μm, two side polished |             |       |  |

| T2051 | 13/10/2003-20/10/2003 | Si 520 um two sido polisbod                      | 20          | 38    |  |

| T2052 | 13/10/2003-20/10/2003 | Si 520 $\mu$ m, two side polished                |             |       |  |

| T2061 | 20/01/2004-30/01/2004 | Si 520 um two sido polisbod                      | 20-24       |       |  |

| T2062 | 20/01/2004-30/01/2004 | Si 520 $\mu$ m, two side polished                |             |       |  |

| T2071 | 20/01/2004-30/01/2004 | Si 520 μm, two side polished                     | 15-17       | 37-40 |  |

| T2072 | 20/01/2004-30/01/2004 | Si 520 µm, two side polisited                    | 13-17 37-40 |       |  |

| T2081 | 9/02/2004-20/02/2004  | Si 520 μm, two side polished                     | 15-17       | 37-40 |  |

| T2082 | 5/02/2004-20/02/2004  | Si 520 µm, two side polished                     | 15-17       |       |  |

## **Dipstick Tests: Twin-SIS Mixer Pump Level** f = 613 GHz

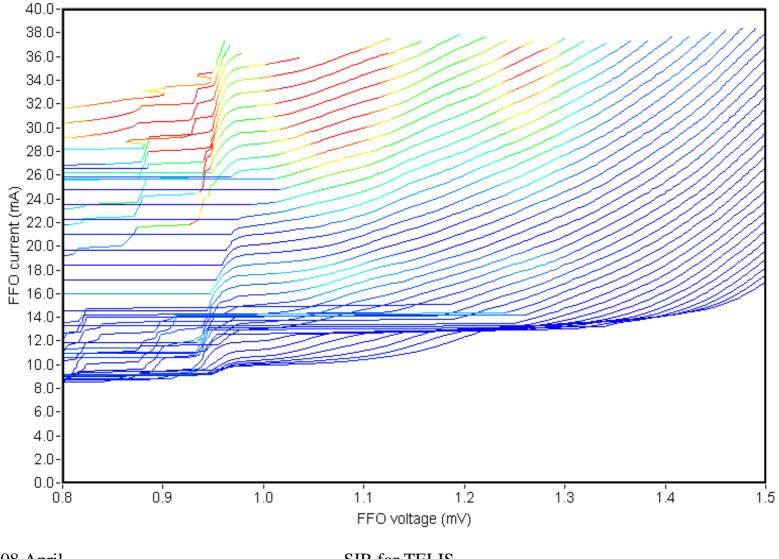

## **Dipstick Test: FFO Power Range**

SIR for TELIS

## **Dipstick Test: FFO Power Range**

## FTS Test: DDA Single-SIS Mixer

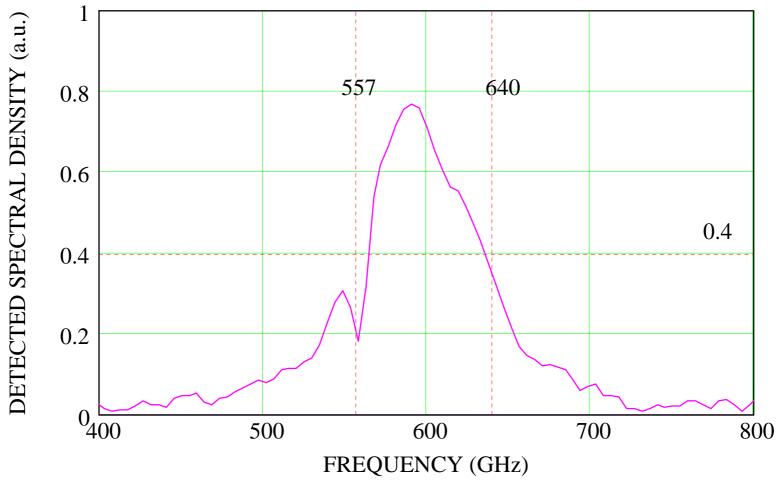

FTS Response of Sigle-SIS DDA Mixer T201111B

SIR for TELIS

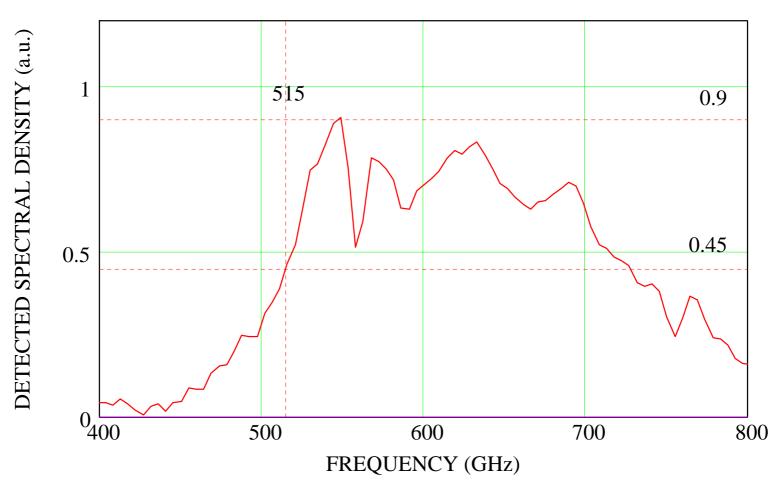

## FTS Test: DDA Twin-SIS Mixer

#### FTS Response of Twin-SIS DDA Mixer T202111R

SIR for TELIS

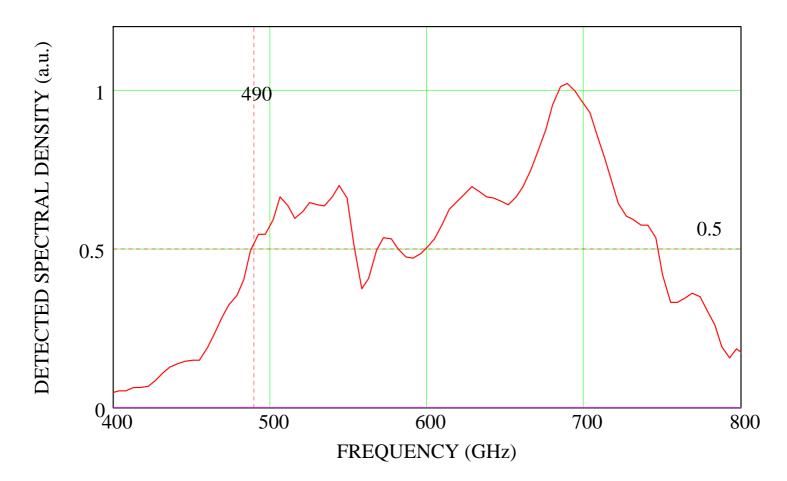

## FTS Test: DSA Twin-SIS Mixer

FTS Response for Twin-SIS DSA Mixer T202111T

SIR for TELIS

## Simulation vs. Test: Pump of Harmonic Mixer

## **T<sub>RX</sub> Test: brief arrangement of new cryostat**

## Preliminary Noise Breakdown

- Y-factor 1-1.3 dB @ 600-630 GHz

- 50 μm beam splitter (BS) transparent 65% @600 GHz; T<sub>cold</sub> rises from 80 K to 156 K

- TRX corrected for BS is 250-380 K

- Dewar window & two infrared filters T = 50%

- IF coupling -2.5 dB @ IF=1.5 GHz

- Final estimate 100-120 K (DSB)

- NOTE: Cooling might be insufficient

- Production of circuits is going satisfactory

✓ Reproducible small area (0.8 μm<sup>2</sup>) SIS junctions

- Twin SIS covers band 520-680 GHz

✓ Flat response has been achieved

- Single-SIS as a narrow-band option

✓ Single-SIS is OK for band 600-650 GHz

- Noise Temperature Preliminary Estimate

✓ Known corrections give 120K (DSB) at IF=1.5 GHz

## T2 chips selected for further receiver test

Summary of chips selected for receiver test

| Sample  | Type<br>(design code) | Expected<br>full<br>performance<br>band<br>(GHz) | FTS<br>band<br>(GHz) | SIS Mixer(s)                      |                    |                                    |                                                                   | FFO                              |                                      |

|---------|-----------------------|--------------------------------------------------|----------------------|-----------------------------------|--------------------|------------------------------------|-------------------------------------------------------------------|----------------------------------|--------------------------------------|

| ID      |                       |                                                  |                      | R <sub>N</sub><br>SIS / HM<br>(Ω) | Q<br>Rj/Rn<br>a.u. | I <sub>CL</sub><br>zeroing<br>(mA) | Pump range f <sub>1</sub> -f <sub>2</sub><br>of SIS / HM<br>(GHz) | I <sub>step</sub><br>max<br>(mA) | I <sub>CL FFO</sub><br>range<br>(mA) |

| T201208 | F2-D2-HMT-4           | 500-650                                          | 500-550,600-670      | 17.3/6.38                         | 27/25              | 50-74-101                          | 480-650/500-700                                                   | 21                               | 11-20                                |

| T204102 | F1-S2-HM-4            | 570-650                                          | 480-520,570-800      | 22.4/11.8                         | 26/23              | 89                                 | 550-700/550-650                                                   | 37                               | 22-33                                |

| T201105 | F1-D2-HM-4            | 600-625                                          | 600-700              | 9.56/4.11                         | 14/23              | 19-55-80                           | 480-630/620-670                                                   | 32                               | 25-29                                |

| T201103 | F2-D2-HM-4            | 500-550<br>580-630                               | 470-700              | 8.81/5.41                         | 26/7               | 34-68-88                           | 470-630/520-700                                                   | 39                               | 15-23                                |

| T201108 | F2-D2-HM-4            | 500-560<br>600-640                               | 600-730              | 10.83/6.08                        | 25/17              | 36-75                              | 480-640/520-710                                                   | 32                               | 14-26                                |

| T201215 | F2-S2-HMT-4           | 470-560                                          | 460-550              | 10.88/6.54                        | 22/26              | 43-80-99                           | 440-640/530-700                                                   | 18                               | 17-24                                |

| T201219 | F2-S2-HM-4            | 480-560                                          | 450-550              | 10.52/5.8                         | 35/37              | 36-66-112                          | 480-557/540-690                                                   | 25                               | 17-24                                |

## Conclusion

- 3 concepts of PL SIR for TELIS have been proposed; 2 of them experimentally proven.

- SIR for TELIS has been developed, fabricated and preliminary tested.

- All main TELIS parameters are satisfied.

- A number of T2 chips with suitable parameters are selected for further RF measurements.

- Design and parameters of FFO and HM were optimized for TELIS.

- Possibility to operate a PL SIR remotely has been demonstrated.